主要研究成果1:针对二维半导体器件界面缺陷导致的性能劣化和功能受限问题,提出在二维半导体异质结间引入范德华间隙调控的方法,通过精准调节亚纳米尺度范德华间隙尺寸和间隙物,抑制了缺陷能态与沟道的耦合,构建新型电子器件和光电子器件。

二维半导体原子级厚度使得界面因素显著影响器件性能,深入理解界面态对叠层器件性能的影响机制,并实现有效调控,阐明沟道材料厚度、介电层厚度、电极接触、异质界面质量等因素对叠层器件的可靠性和稳定性的影响规律,可以有效解决二维半导体器件界面缺陷导致的性能劣化和功能受限问题。针对这一关键问题,项目负责人基于二维半导体物性调控开展了探索性工作,实现了对二维材料能带的精细调控;设计了非平面栅极结构,增强了器件栅极控制能力,大幅度提升了器件的电学性能。

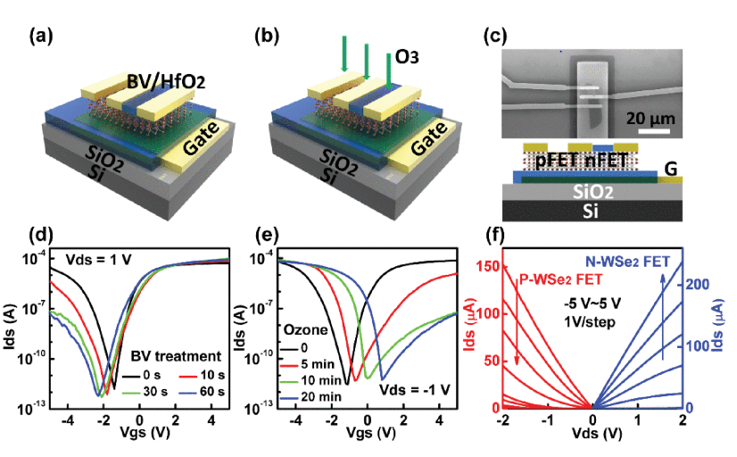

1)表面功能化实现二维半导体PN掺杂:随着二维半导体晶体管研究和制备工艺的发展,已经实现了一些互补反相器的制备,但仍存在几个关键挑战。首先,使用单一二维材料同时获得n型和p型半导体场效应晶体管相当困难。同时,二维材料互补反相器的性能有待提高,如噪声容限低、静态功耗大、电压增益低于20等。此外,二维材料互补反相器的制备工艺也需进一步简化。以往报道通常利用气相掺杂和重叠顶栅器件结构来控制WSe2的导电类型,然而,由于缺少轨到轨性能,所得互补反相器的电压增益相对较低。采用有机电荷转移分子掺杂的WSe2互补技术,电压增益超过30,但需要多次沉积Ag和Pt电极,这大大增加了制备的复杂性。因此,开发一种不仅在单个WSe2薄片上具有出色电学特性,而且制备工艺简单的互补反相器至关重要。团队通过在单个薄片上采用埋栅结构展示了基于WSe2的互补反相器。简而言之,使用苄基紫精作为表面电子转移供体,对WSe2晶体管进行n型掺杂。通过使WSe2薄片暴露于臭氧中增强其空穴导电性,臭氧因其较大的氧化还原电位而成为有效的电子受体。此外,采用高k电介质的埋栅结构来改善栅极的静电控制,同时也便于对WSe2沟道层进行表面调制。通过在互补反相器技术中使用BV和埋栅结构,开发了一种无需多次电极沉积或顶栅的简单制备工艺。所得互补反相器表现出超过32的高电压增益,具有优异的电压传输特性、全逻辑摆幅和接近0.5电源电压(Vdd)的优异噪声容限(在5V的Vdd下)。相关论文发表在IEEE Electron Device Letters, 2020, 41, 944。

图1 基于WSe2构筑互补性电路。(a)-(b) WSe2互补反相器的制备过程。(c) WSe2互补反相器的扫描电子显微镜图像及横截面示意图(蓝色部分为HfO2,黄色部分为电极)。(d)-(e) 经过不同BV(苄基紫精)处理时间和臭氧处理时间的WSe2场效应晶体管(FET)的转移特性。(f) 经过60秒BV处理和20分钟臭氧处理WSe2场效应晶体管的输出特性。

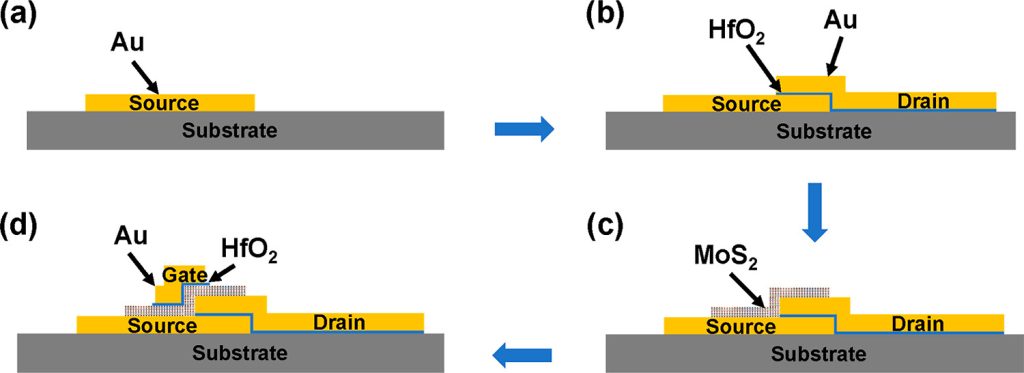

2)二维半导体晶体管Ω形栅极结构设计:非平面栅极架构因其出色的静电控制能力,为提高栅极可控性提供了有效策略,其性能远超传统平面体技术。随着晶体管尺寸的不断缩小,该结构通过实现陡峭的亚阈值摆幅(SS),为抑制短沟道效应提供了可能。环绕式栅极结构相比平面结构提供了更优越的静电栅极控制。因此,可以在保持器件性能提升的同时抑制漏电流。然而,这种结构需要复杂的制造工艺。换言之,静电可控性的提升与制造复杂性之间存在权衡。在最大化静电约束的同时最小化制造复杂性的另一种解决方案是采用Ω形栅极架构,该架构由于栅极可控性的提高而具有优异的电性能。在非平面Ω形栅极配置中,相对于沟道体积,被栅极包围的半导体表面有所增加。静电控制的改善为具有超短沟道长度(Lch)的场效应晶体管提供了低泄漏和低功耗。然而,5纳米节点的硅晶体管需要小于3纳米的体厚度以实现理想的沟道控制。在如此薄的体厚度下,传统半导体受到迁移率或量子电容的挑战。传统沟道材料表面的缺陷会散射电荷载流子,导致电流流动不佳。此外,源极到漏极的量子隧穿或可变性显著,并恶化了缩放器件中的开关比。另一方面,在晶体管沟道长度缩小时,应用其他潜在材料替代硅是有前景的。二维材料是具有原子厚度的晶体薄片。由于其表面平坦且没有悬挂键,载流子不易散射,可以相对自由地通过沟道流动。因此,如二硫化钼等2D材料代表了大面积电子器件中的终极缩放晶体管。先前报道的工作主要集中在缩短平面维度以实现超短沟道长度上,这展示了优越的开态沟道电流,并在某些方面验证了与硅基晶体管相当的性能。然而,所报道的平面MoS2场效应晶体管缺乏合理的栅极耦合设计,因此电性能不足。针对这个问题,团队制造了具有Ω形栅极配置的非平面MoS2场效应晶体管。由于栅极配置的合理设计增强了静电耦合,这些晶体管表现出稳健的性能,具有高电流0.89 mA/μm、高开/关比 107 和低阈值电压。基于MoS2晶体管的出色夹断和电流饱和特性,NOT门和NOT-AND(NAND)门电路完全组装在单个MoS2薄片上。NOT门反相器在4.5 V的应用电压(VDD)下表现出26.6的电压增益,并且噪声容限接近0.5 VDD,几乎达到理想值。所构建的NAND门表明了晶体管的通用功能。该策略表明了针对具有硅基晶体管竞争性能的二维电子器件的代表性栅极几何设计。相关论文发表在Science Bulletin, 2021, 66, 77。

图2 具有Ω形栅极的MoS2晶体管的制造工艺示意图。(a) 将少层MoS2薄片转移到带有Al2O3介电层的Ga2O3纳米线上,并将其蚀刻成固定宽度为1微米的形状。(b) 通过电子束光刻定义源极/漏极接触区域,然后通过热蒸发和剥离工艺沉积Cr/Au(10纳米/70纳米)。(c) 采用原子层沉积(ALD)技术沉积厚度为15纳米的Al2O3顶栅介电层。(d) 通过电子束光刻定义顶栅电极区域,然后通过沉积Cr/Au(10纳米/70纳米)和剥离工艺完成制作。(e) 晶体管的横截面示意图。(f) 栅极处的电场分布。

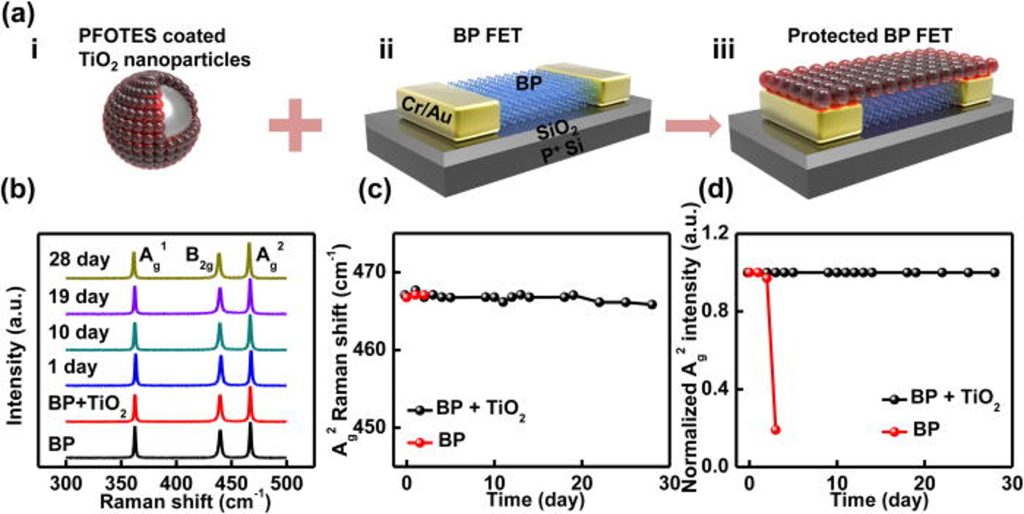

3)具备超疏水保护层的场效应晶体管设计:二维(2D)材料凭借其独特的电学特性和原子级厚度,已成为未来高性能电子器件领域的研究热点。黑磷(BP)具备p型特性、适中的能带隙(0.3~2.0 eV)和较高的载流子迁移率(~1000 cm²/Vs)是构建低功耗互补电路的理想材料。然而,由于水和氧气的协同作用,黑磷在空气中极易氧化,导致其电学性能不稳定。尽管已有多种钝化策略被报道,例如通过薄膜沉积形成的氧化层、六方氮化硼(h-BN)的物理覆盖以及有机封装,但这些方法各有局限。传统的异质集成薄膜沉积工艺(如原子层沉积和电子束蒸发)往往会在界面处引入额外的缺陷,从而降低其电学性能。六方氮化硼薄片的物理转移不仅耗时且难以规模化。此外,有机封装策略中,有机层与通道层之间的电荷转移会导致阈值电压偏移,且有机材料在长期使用中会发生降解,导致封装层失效。因此,现有的钝化策略要么难以规模化,要么会与通道层相互作用,影响电学性能。此外,在复杂的水环境中,黑磷的稳定性也会受到严重影响。 鉴于此,开发一种稳健、可扩展且无损的集成方法对于实现高性能黑磷器件至关重要。基于这一背景,研究团队成功制备了能在恶劣环境条件下(相对湿度60%、温度约35°C)具有长期稳定性的黑磷场效应晶体管(FET)。该器件通过超疏水保护层有效隔绝了水分的影响。钝化层由氟烷基硅烷包覆的二氧化钛纳米颗粒组成,可以采用浸涂法制备。与可能对黑磷造成破坏的传统制造工艺相比,这种溶液加工方法是一种低能耗且无损的集成策略,不会对黑磷表面造成降解。超疏水钝化层不仅确保了黑磷晶体管在环境大气中对水、盐酸(HCl)和氢氧化钾(KOH)的稳定性。而且在潮湿空气中暴露28天后,器件性能变化率低于20%。即使在大气环境中暴露60天后,器件仍能正常工作。此外,这种策略还为其他二维材料晶体管提供了一种超疏水保护层,使其能够抵御水基恶劣环境的威胁,并在环境条件下保持器件的固有电学性能。相关论文发表在Applied Physics Letters, 2020, 117, 111602。

图3 制备工艺和拉曼稳定性表征。(a) 以PFOTES包覆的TiO₂纳米颗粒作为保护层的BP(黑磷)晶体管的示意图。(b) 在环境条件下,PFOTES包覆的TiO₂纳米颗粒封装的BP的拉曼光谱。(c) 不同老化时间下的拉曼位移和(d) Ag₂模式的归一化峰强度。黑色点表示PFOTES包覆的TiO₂纳米颗粒封装的BP(黑磷),红色点表示裸露的BP。

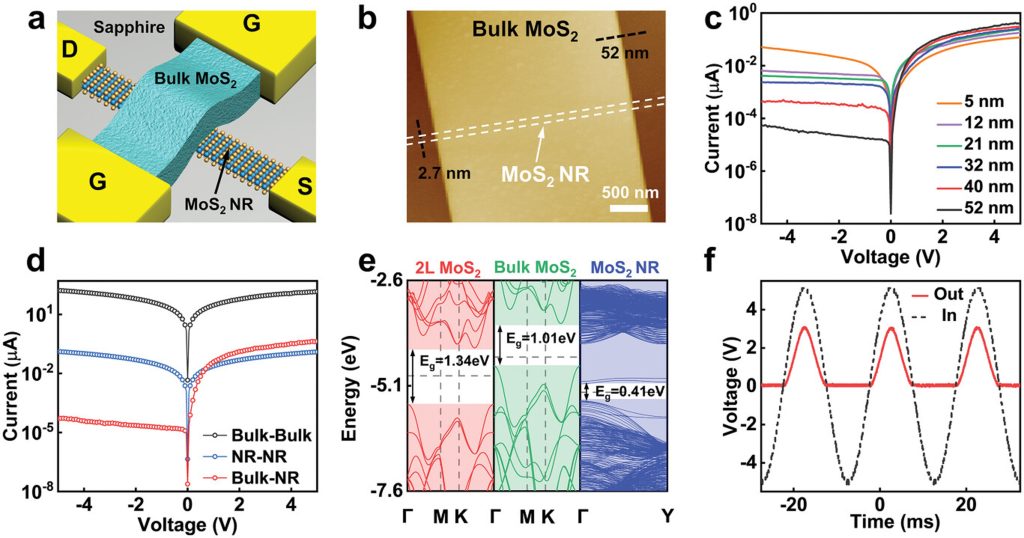

4)块体MoS₂/MoS₂纳米带(NR)同质结:为了满足日益复杂的应用需求,精确定制金属氧化物半导体场效应晶体管(MOSFET)的功能特性变得愈发关键,而这一目标在很大程度上依赖于掺杂工程。对于传统的硅基MOSFET而言,为了实现理想的电气性能,漏极-沟道和源极-沟道结处需要超陡的掺杂浓度分布,这使得原子尺度效应在器件性能中扮演了愈发重要的角色。尽管通过引入创新的晶体管架构,例如鳍式场效应晶体管(FinFET)和全耗尽型绝缘体上硅晶体管(FD-SOI),能够在一定程度上缓解由随机掺杂波动引起的MOSFET性能变异,但电荷的离散性和物质的颗粒性所导致的统计变化是不可避免的。在传统硅基器件的微型化进程中,彻底消除随机掺杂波动问题仍然是一个亟待解决的挑战。为了让持续缩小尺寸、保持理想的栅极可控性和高密度集成能够同时实现,沟道材料的厚度需要进一步减小。当硅薄膜的厚度降低到10 nm以下时,线条边缘粗糙度和表面粗糙度会导致载流子迁移率降低和寄生接触电阻增加。在这种背景下,像二硫化钼(MoS2)这样的二维材料以其原子级厚度为制造超薄高性能晶体管和电子电路提供了一种极具潜力的解决方案。二维材料不受表面粗糙度引起的载流子散射的影响,这使其能够克服硅基MOSFET所面临的沟道厚度变化的限制。此外,二维材料的横向限制已被证明是调节能带的有效方法。例如,石墨烯作为一种零带隙材料,可以通过沿特定晶格方向切割成纳米带(NR)来产生可测量的带隙。类似地,先前的研究表明,由于量子限制效应,通过调节MoS2纳米带的物理尺寸,可以轻松地调节MoS2的能带结构。与石墨烯不同,MoS2的带隙缩放与纳米带宽度成正比,这与理论预测一致。团队通过调节MoS2纳米带的物理尺寸实现了能带结构的调控并构建了具有突变能级变化的块体MoS2/MoS2纳米带同质结,其展现出1.77的理想因子和高达104的整流比。通过使用块体MoS2和MoS2纳米带作为栅极和载流子传输通道,团队制备了MoS2金属-半导体场效应晶体管(MESFET)。这些MESFET展现出几乎可以忽略的栅极迟滞现象,亚阈值摆幅(SS)低至120 mV/dec。此外,该器件展现出稳健的性能,具有46 μA/μm的高开启态电流、-1.08 V的阈值电压(VTH)以及易于饱和的特性。与先前报道的二维异质结MESFET相比,MoS2 MESFET不仅避免了不可控的本征掺杂过程,而且与现有技术兼容。除此以外,团队在蓝宝石基底上组装了基于MoS2 MESFET的反相器,其展现出15.4的电压增益和接近理想的噪声容限(电源电压的83%)。由此可见,团队所提出的策略为基于同种材料衍生物制造晶体管开辟了新的可能性。相关论文发表在Advanced Electronic Materials, 2021, 7(11), 2100703。

图4 块体MoS₂/MoS₂纳米带(NR)同质结的电学性能。(a) 在蓝宝石基底上制备的MoS₂金属-半导体场效应晶体管(MESFET)的示意图。(b) 块体MoS₂/MoS₂纳米带同质结的原子力显微镜(AFM)图像。(c) 随块体MoS₂厚度变化的MoS₂同质结整流特性演变。(d) 块体MoS₂纳米片、MoS₂纳米带通道以及块体MoS₂/MoS₂纳米带同质结的电流-电压曲线。(e) 双层(2L)MoS₂、块体MoS₂以及基于非紧密接触模型的2L MoS₂的密度泛函理论(DFT)计算能带结构。(f) 块体MoS₂/MoS₂纳米带同质结的动态整流特性。

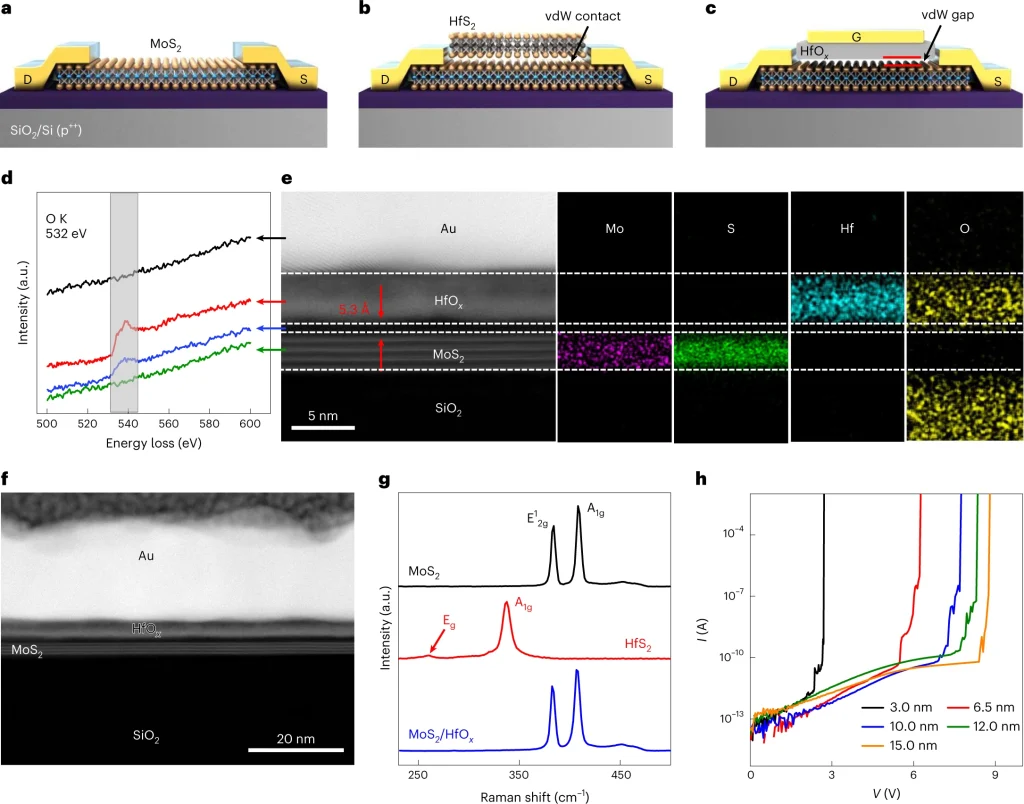

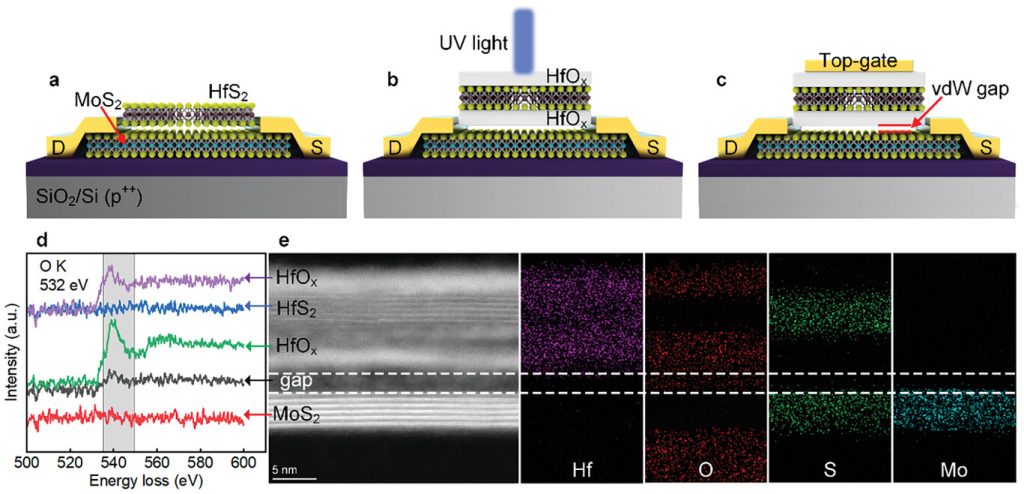

5)氧积累在介电界面处扩大范德瓦尔斯间隙:层状过渡金属硫化物,特别是二硫化钼(MoS₂),被视为构建通道长度接近1 nm场效应晶体管的潜力材料。为了实现这类晶体管的高开启电流和低操作电压目标,关键在于在MoS₂表面沉积超薄且具备高κ值的介电材料,这些材料需拥有极小的等效氧化物厚度。然而,MoS₂表面因缺乏活性悬挂键而增加了沉积难度,如原子层沉积(ALD)等策略常需引入预先制备的颗粒作为成核点,以在MoS₂上形成化学键。这一过程中新化学键的形成及电子交换会促使MoS₂与介电材料间电子密度的重新分布,形成强相互作用。为了减轻对MoS₂通道的损伤并保持其性能,可以适当采用润湿性的吸附剂。但SiO₂、Al₂O₃和HfOₓ这类无定形氧化物介电材料,因其界面质量不佳及高缺陷密度,往往导致晶体管表现出显著的迟滞现象。尽管晶体介电材料能形成更光滑的界面并降低缺陷密度,但其合成工艺却相对复杂。因此,如何在不牺牲MoS₂性能的前提下完成高质量的栅极介电层的沉积,仍是一个待解难题,导致实际器件性能尚未达到理论预期。研究表明,调整石墨烯费米能级以远离无定形介电材料中缺陷能带,可增强石墨烯晶体管的稳定性,意味着减弱半导体与介电材料的相互作用能提升电学性能。除了能带偏移,相邻原子和分子间的范德华力(vdW)也是影响接触材料性质的关键因素,其强度与两材料间距密切相关。特别地,当通道与介电材料间距小于3 Å时,介电材料会诱导间隙态出现在通道带隙中;间距超过3 Å时,则形成物理吸附界面,此时两材料的电子性质在吸附过程中几乎不受影响,电子重新分布极少。因此,增大间距成为解耦相互作用并保留材料固有性质的有效方法。基于以上背景,团队提出了一种利用臭氧处理HfS₂/MoS₂堆叠层,在HfOₓ与MoS₂间形成vdW间隙的新方法。处理过程中,HfS₂薄片转化为HfOₓ介电材料,同时界面处氧迁移的高势垒导致氧积累,将vdW间隙扩大至5.3 Å。间隙减弱了介电/通道界面的相互作用,保护了MoS₂通道的固有特性。此外,扩大的vdW间隙作为电荷载流子注入介电材料的屏障,减少了载流子散射。该技术避免了在MoS₂表面进行破坏性的溅射或ALD沉积。基于此方法制造的MoS₂范德华间隙栅控(VGG)晶体管,展现出无迟滞操作、高达10⁸的开关比、低于10⁻⁷ μA·μm⁻¹的栅极漏电流及接近理想玻尔兹曼极限的平均亚阈值斜率(63.1 mV·dec⁻¹)。除此以外,团队还展示了基于多个VGG晶体管的NOT、OR和AND逻辑门。相关论文发表在Nature Electronics, 2022, 5(12): 849-858.

图5 (a) MoS₂薄片在SiO₂/Si基底上,带有Cr/Au(10/50 nm)接触电极。(b) HfS₂薄片堆叠在MoS₂通道上。(c) 通过臭氧处理形成HfOₓ介电层,随后沉积顶栅电极。S:源极;D:漏极;G:栅极。(d) 不同层O K核层边缘的电子能量损失谱叠加。(e) 截面透射电子显微镜图像及元素分布。(f) 截面TEM图像显示栅极结构的均匀性。(g) 器件不同区域的拉曼光谱。(h) 介电层的击穿特性。

6)Ω形埋栅晶体管设计:随着晶体管尺寸的持续微缩,传统平面场效应晶体管(FET)面临着栅极静电控制能力下降、电气性能劣化以及功耗增加等严峻挑战。为解决这些难题,非平面结构晶体管如鳍式场效应晶体管(FinFET)和环绕栅极场效应晶体管(GAAFET)应运而生,它们通过优化栅极结构显著提升了栅极控制能力和漏电流抑制效果。近年来,二维材料因具有优异的栅极控制能力和载流子迁移率特性而备受关注。以二硫化钼(MoS2)为代表的二维材料,其弱散射效应使其在高电流密度应用场景中展现出卓越性能。已有研究证实,MoS2晶体管的电性能可与传统硅基晶体管相媲美,这表明其在下一代先进电子器件中具有巨大应用潜力。在栅极结构创新方面,Ω形栅极架构作为一种非平面结构设计,通过增强局部栅极控制能力为高性能晶体管研发提供了新思路。然而,其在器件制备过程中往往面临高质量栅极介电层沉积的技术挑战。针对这一问题,埋栅结构提供了一种有效解决方案。团队开发了一种基于银纳米线(Ag NW)埋栅的Ω形双栅MoS2晶体管。实验结果表明,该器件展现出优异的电学特性:室温下的开关电流比高达10⁸,阈值摆幅(SS)约为76 mV/dec。通过器件集成,成功构建了反相器和NAND门电路。反相器在VDD=2 V时实现高达36的电压增益,噪声容限接近0.87 VDD。这为基于二维材料的高电流晶体管开发提供了一种创新性解决方案,有助于推动二维材料在高性能电子器件领域的应用。相关论文发表在IEEE Transactions on Electron Devices, 2022, 69(2): 816-819。

图6 (a) Ω形MoS₂晶体管的顶视图。(b) 器件的截面视图。(c) 栅极确定时的电场分布(VTG = 5 V 和 VBG = 60 V)。(d) 平面和非平面电场分布(VTG = 5 V)。(e) Ω形晶体管的扫描电子显微镜图像。(f) 少层MoS₂通道的拉曼光谱。

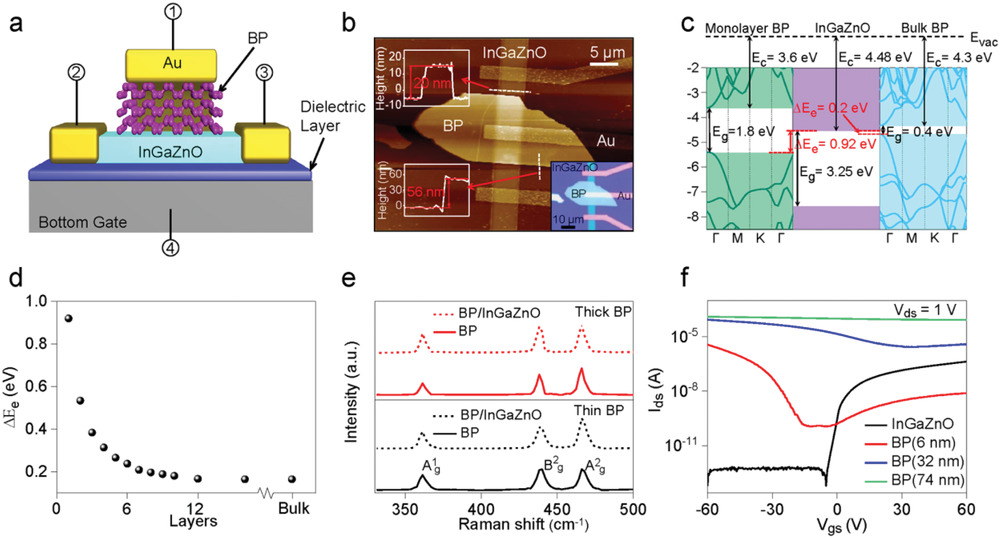

7)非晶金属氧化物半导体TFET和JFET的器件实现:非晶态金属氧化物半导体(AMOS)因其在透明性、高载流子迁移率、环境稳定性、机械柔韧性和低温工艺可行性等方面的优势而备受关注。其中,铟镓锌氧化物(InGaZnO)就是典型的非晶态金属氧化物半导体材料。AMOS已被广泛应用于金属-绝缘体-半导体场效应晶体管(MISFET)中,并在主动矩阵显示器(AMD)中起到了不可替代的作用。随着时代不断发展,市场对更高像素密度和更低功耗的AMD以及对尺寸更小且性能更优的MISFET的需求不断增长。尽管有很多研究着重放在材料选择和晶体管微型化工艺的优化上,但尺寸不断缩小的MISFET仍面临两大主要挑战:首先,MISFET的工作电压无法随尺寸缩小而相应降低,这源于器件的静电控制能力的下降以及热电子发射机制对MISFET开启特性所施加的基本限制,即亚阈值摆幅(SS)值为2.3 kBT/q(其中q、kB和T分别表示基本电荷、玻尔兹曼常数和绝对温度)。其次,不均匀的介电层/AMOS界面处的陷阱态会干扰载流子传输行为,导致载流子迁移率受限并产生严重的迟滞现象。很少有研究表明传统的MISFET能够克服因持续缩小尺寸而产生的严重挑战。因此,探索不同的晶体管机制以满足消费者对高性能、低功耗的需求显得尤为重要。在此背景下,隧穿场效应晶体管(TFET)和结型场效应晶体管(JFET)被认为有望取代传统的MISFET,成为薄膜晶体管技术的下一代解决方案。与依赖热电子发射(TE)机制的MISFET不同,TFET采用带间隧穿机制,通过重掺杂的p-n结实现载流子隧穿,从而突破了室温下SS值为60 mV/dec的限制,展现出克服短沟道效应和实现超低功耗的潜力。此外,JFET可以通过调节p-n结耗尽区实现开关,无需沉积介电层,这极大避免了InGaZnO/介电界面处电荷俘获的负面影响。当去除栅极介电层后,JFET类似于具有无限栅极电容的MISFET,在亚阈值区域的表现有望超越MISFET。然而,非晶态AMOS的结构较为松散,使得实现超陡掺杂剖面的方法极具挑战性。尽管AMOS基TFET和JFET备受关注,但尚未在实验中得到充分验证。二维原子晶体因其原子级厚度和无悬挂键表面,在TFET和JFET应用中展现出巨大潜力。这些特性使其能够在不受晶格失配限制的情况下构建多样化的异质结。然而,利用二维材料的优越特性来提升AMOS晶体管性能的研究仍较少。团队系统研究了垂直堆叠的二维黑磷(BP)/InGaZnO范德华(vdW)异质结二极管的电学特性。由于BP的p型掺杂水平高度依赖于其厚度,可以通过简单的BP厚度调节实现正向整流二极管、反向整流二极管和齐纳二极管之间的功能切换。利用厚BP作为电子载流子源,InGaZnO作为导电通道,团队制备了InGaZnO TFET,其最小亚热离子亚阈值摆幅(SS)值为11 mV/dec。该器件在室温下表现出明显的负微分电阻现象,这表明在垂直堆叠的厚BP/InGaZnO界面处存在带间隧穿。此外,团队还通过构建薄BP/InGaZnO vdW p-n结制造了InGaZnO JFET,其中薄BP栅极实现了良好的n型晶体管特性,具有超过10⁵的高开关电流比、23.5 cm²/Vs的高场效应迁移率、可忽略的迟滞现象以及SS值为83 mV/dec。这些结果有力地证明了基于BP/InGaZnO vdW异质结的InGaZnO TFET和JFET应用于低功耗集成电路中的巨大潜力。相关论文发表在Advanced Electronic Materials, 2020, 6(8): 2000291。

图7 异质结器件示意图及材料表征。(a) 基于BP/InGaZnO范德华异质结的InGaZnO晶体管示意图。(b) BP/InGaZnO异质结的原子力显微镜图像。插图展示了一个典型的BP/InGaZnO异质结的光学图像。(c) BP的能带结构,包括电子亲和能和带隙,这些数据来自密度泛函理论(DFT)计算。(d) BP的价带顶与InGaZnO的导带底之间的最小有效带隙。(e) 纯BP和BP/InGaZnO异质结的拉曼表征。(f) InGaZnO和BP场效应晶体管的转移曲线。

8)纳米级器件的设计:场效应晶体管(FET)的尺寸已经从微米级别显著缩减至纳米级别,旨在将更多功能组件高度集成于单一芯片之上。随着尺寸的持续缩减,传统的硅(Si)基FET遭遇了众多挑战。为了保持有效的栅极控制并缓解短沟道效应的不良影响,传统硅FET的沟道厚度必须小于沟道长度(L)的三分之一。但当器件的特征尺寸步入纳米尺度时,硅半导体器件的表面与内部缺陷显著增多,这不仅阻碍了其性能的进一步提升,也对制造工艺提出了更高的要求。与此同时,二维(2D)材料凭借其原子级的厚度及独特的电学属性,逐渐崭露头角,被视为下一代纳米电子器件的潜力之星。由单原子层构成的二维材料,可通过化学修饰和功能分子吸附等手段进行精确调控,从而实现性能与应用的定制化。这种高度的可调性为二维材料在纳米电子学领域的广泛应用开辟了全新的道路。尽管二维材料领域取得了诸多突破,但目前FET电流的提升仍主要依赖于沟道长度(L)的缩减。对于平面结构的FET而言,其沟道长度(L)受限于传统微纳加工技术的精度,使得制造10 nm及以下尺寸的FET面临巨大挑战。为了打破这一瓶颈,制造垂直结构的FET成为了一种极具潜力的解决方案。例如,通过化学气相沉积(CVD)合成的单层二硫化钼(MoS₂)在10 nm垂直沟道FET中,于源漏电压(Vds)为0.5 V和源栅电压(Vgs)为16 V的条件下,实现了21.5 μA/μm的电流密度。此外,通过调整云母片的厚度获得小于10 nm的MoS₂垂直沟道FET,并在Vds为3 V和Vgs为5 V的条件下记录到了高达318 μA/μm的开启态电流。相较于平面结构,垂直结构的沟道长度可通过间隔层的厚度轻松调控,为纳米级器件的制造提供了极大的便利。然而,为确保器件的可靠性和性能,必须严格监控缺陷的产生。低频噪声(LFN)作为纳米级器件性能和应用的潜在制约因素,其广泛存在不容忽视。LFN作为一种非破坏性的检测手段,能够有效评估电活性缺陷的存在。先前的研究已对单层MoS₂晶体管的低频电子噪声进行了探索,实验中所用器件的长度(L)为1.71 μm,宽度(W)为3.32 μA/μm。同时,关于CVD双层MoS₂ FET的LFN也有所讨论,并在频率(f)为100 hz时达到了最小的归一化漏极电流功率谱密度(WLSID/ID²)为3.1×10⁻¹⁰ μm²/hz。然而,对于MoS₂ FET而言,LFN的分析主要集中于长沟道器件,而针对纳米级MoS₂ FET的研究仍相对匮乏。团队通过在源极与漏极电极之间插入HfO₂间隔层,成功制造了具有不同沟道长度的纳米级MoS₂垂直FET(VFET)。此时,沟道长度由HfO₂的厚度决定,从而实现了10 nm长的MoS₂ VFET的制造。10 nm MoS₂ VFET在Vds为3 V和Vgs为6 V的条件下,展现出了高达537 μA/μm的电流密度。团队在纳米尺度上对LFN进行了详尽的研究。研究表明,LFN的结果与经典的1/f噪声模型相符,其根源在于载流子数量波动(CNF)。团队还探究了纳米级器件中LFN随沟道长度的变化规律,验证了所获得纳米级晶体管的可靠性以及制造策略的可行性。结果表明,短沟道MoS₂ VFET中的LFN与1/L呈正相关。此外,团队还评估了归一化噪声水平与器件面积以及体积氧化物陷阱密度与1/L之间的关系。总体而言,本研究不仅成功实现了纳米级器件的制造,还对其LFN进行了深入剖析,为纳米电子学的发展提供了重要的理论与实验支撑。相关论文发表在ACS Applied Nano Materials, 2024, 7(17): 21057-21062。

图8 (a–d)通过HfO₂定义器件通道的MoS₂垂直场效应晶体管(VFET)的制备工艺流程。

9)具有范德华间隙的浮栅存储器实现:闪存因其高存储容量而被广泛应用于非易失性存储领域。然而,传统闪存的核心结构——浮栅(FG)架构,正面临着诸多挑战。这种架构由沟道层和数据浮栅层组成,二者通过隧穿层和控制氧化层完全电隔离。尽管如此,浮栅晶体管有限的保持时间限制了其作为非易失性存储器的潜力,这主要源于栅极结构的复杂性以及浮栅层中电荷的泄漏问题。近年来,二维层状过渡金属二硫化物(如二硫化钼,MoS₂)凭借其理想的原子级平整表面和超薄层结构,展现出在内存计算系统中的巨大潜力。这些材料通过有效的静电控制,能够显著减少寄生缺陷捕获,同时支持存储系统的进一步缩放。然而,MoS₂表面的非悬挂键特性使其难以沉积高质量的介电层,这不仅增加了制造的复杂性,也限制了器件的存储性能。尽管已有基于MoS₂的非易失性浮栅存储器的报道,但操作电压与保持时间之间的权衡问题依然存在,这主要取决于浮栅结构中介电层的厚度和质量。在MoS₂表面沉积超薄高κ介电层是一种潜在的解决方案,它可以实现对栅极电势的高可控性,从而延长保持时间。然而,传统的沉积策略(如原子层沉积,ALD)依赖于结合介质(如预处理的颗粒)在二维材料表面形成成核位点,这不可避免地引入杂质,并导致介电/通道界面粗糙或多孔。这种不理想的界面会显著恶化浮栅晶体管的电学性能。此外,隧穿氧化层/通道界面处的陷阱和缺陷会导致存储电荷的逐渐损失,进一步削弱存储器的保持能力。因此,开发高质量的隧穿氧化层以及设计完美的介电/通道界面对于实现低漏电流、避免存储器性能下降至关重要。范德华(vdW)集成策略能够实现无互扩散的理想器件界面工程。此前的研究表明,当vdW距离超过3 Å时,物理吸附现象会显著减少,从而有效避免陷阱辅助隧穿效应。合理设计栅极结构可以轻松最小化漏电路径,使浮栅结构的静电势能够长时间保持,从而轻松调控沟道状态,这为实现可配置的内存内逻辑操作提供了可能。团队通过臭氧处理从HfS₂薄片中获得了高质量的HfOₓ介电层,从而构建了由HfS₂浮栅层及其绝缘氧化物HfOₓ组成的浮栅结构。高密度的电荷被注入到HfS₂浮栅层中,而隧穿氧化层/通道处的vdW间隙有效阻止了漏电。透射电子显微镜(TEM)图像显示,器件形成了高质量且无缺陷的HfOₓ/HfS₂/HfOₓ浮栅结构。团队制造的vdW间隙MoS₂浮栅晶体管展现出稳健可靠的电学性能,具有卓越的保持和耐久特性。相关论文发表在Advanced Functional Materials, 2422120。

图9 隧穿氧化层/MoS₂通道界面的示意图及范德华(vdW)间隙。(a) 在SiO₂/Si(p++)衬底上带有Cr/Au(10/50 nm)接触的背栅MoS₂晶体管,以及堆叠在MoS₂通道上的HfS₂薄片。(b) 通过臭氧处理形成HfOₓ介电层。(c) 顶栅电极的形成。(d) 不同层O K核层边缘的电子能量损失谱(EELS)叠加。(e) 截面透射电子显微镜(TEM)图像及元素分布。

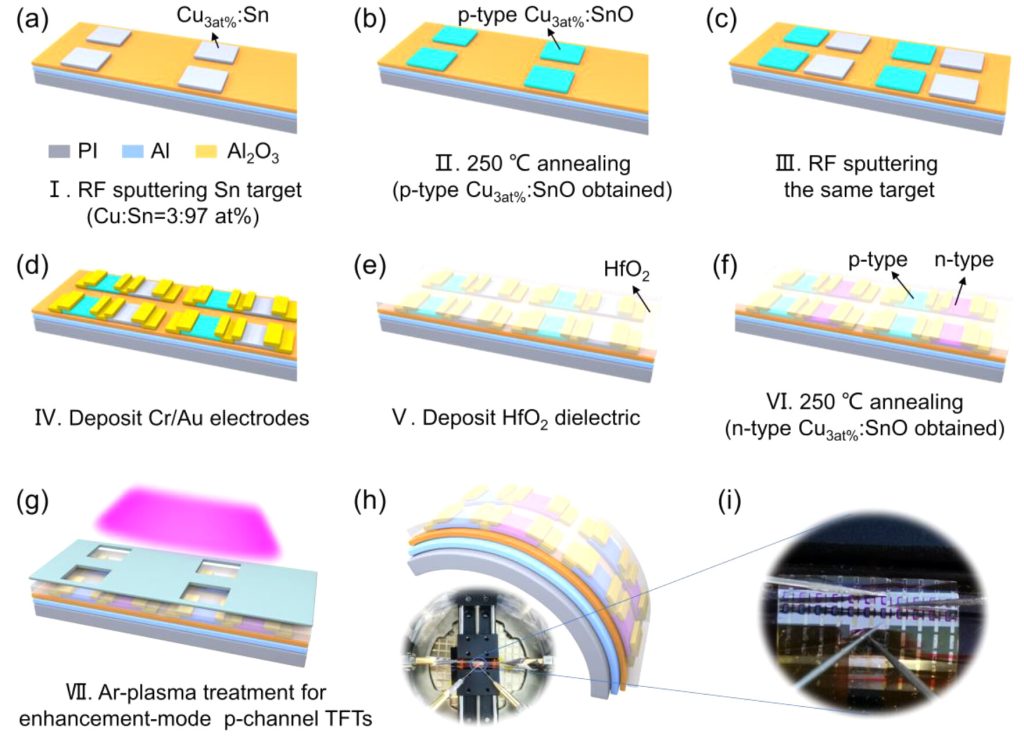

10)用于互补金属氧化物半导体技术实现的掺杂策略:互补金属氧化物半导体(CMOS)逻辑电路具备低功耗、宽噪声容限(NM)以及大规模制造能力等优点,已成为推动集成电路产业发展的关键力量。然而,传统硅基CMOS电路的固有刚性和脆性限制了其在新兴柔性电子领域的应用。相比之下,金属氧化物半导体凭借其高载流子迁移率和在塑料基底上的低温沉积工艺,在柔性电子领域的商业化应用中展现出巨大潜力。然而,多种金属氧化物半导体工艺之间的不兼容性可能导致复杂的布局和高昂的成本,这并不适合商业化应用。SnO的电子结构较为特殊,Sn 5p轨道对导带最小值(CBM)的球形分布贡献以及5s轨道对价带最大值(VBM)的贡献,使其成为唯一能够作为薄膜晶体管(TFT)通道同时传导电子和空穴的双极性氧化物半导体。尽管双极性SnO TFT在CMOS逻辑电路中显示出潜力,但其载流子迁移率低于单极性器件。除此此外,与集成n型和p型TFT且具有明显开关状态的反相器不同,基于双极性SnO的反相器很难完全关闭。因此,开发高性能单极性n型和p型SnO器件的有效策略是必要的。在SnO中,VBM来自杂化的O 2p和Sn 5s轨道,而球形分布的Sn 5s轨道允许高空穴迁移率。同时,CBM主要由Sn 5p轨道组成,部分态密度曲线显示出类似自由电子的带,这有利于电子传输。此外,SnO具有2.7 eV的直接(光学)带隙和0.7 eV的间接(基本)带隙,实现了较小的电离势和较大的电子亲和能,这是p型和n型掺杂所需的条件。鉴于此,通过适当掺杂和调整导电类型的杂质,实现p型和n型SnO TFT是极具前景的。在这样的背景下,团队展示了一种高效的掺杂策略,通过在柔性聚酰亚胺(PI)基底上掺杂Cu来实现p型和n型Cu:SnO TFT。通过在HfO₂封装后对Cu掺杂浓度为3%的SnO薄膜进行退火,获得了n型模式。由于Hf原子的强还原性,靠近Sn空位的O原子会迁移到HfO₂层,这显著抑制了SnO中的p型导电性。此外,间隙Cu⁺可以诱导n型掺杂效应,同时通过去除导带最小值的简并性来提高电子迁移率。因此,n型Cu掺杂浓度为3%的SnO TFT展现出创纪录的高电子迁移率(μₑ,FE)43.8 cm²/V·s和开关电流比(Ion/Ioff)6.8×10⁴。通过在HfO₂封装前对相同的Cu掺杂浓度为3%的SnO薄膜进行退火,可以实现p型TFT,其展现出超高空穴迁移率(μₕ,FE)2.4 cm²/V·s和Ion/Ioff为1.3×10⁴。通过HfO₂封装后的额外氩等离子体处理,可以通过注入的Hf⁴⁺的n型掺杂效应调节器件的阈值电压,以实现增强型器件。基于n型和p型Cu掺杂浓度为3%的SnO TFT,团队构建了柔性互补逻辑电路(反相器、NAND和NOR门)。通过偏置应力和弯曲测试展示了优异的操作稳定性。p型Cu掺杂浓度为3%的SnO TFT的制造与n型器件兼容,这揭示了基于单一金属氧化物半导体实现p型和n型TFT的潜力。相关论文发表在Nano Letters, 2024, 24(4): 1176-1183。

图10 柔性互补反相器的制备。(a) 射频溅射Cu:Sn薄膜阵列。(b) 在大气中退火以获得p型薄膜。(c) 在p型Cu:SnO薄膜附近射频溅射Cu:Sn薄膜阵列。(d) 沉积Cr/Au电极。(e) 沉积HfO₂保护层。(f) 在大气中退火以获得n型Cu:SnO薄膜。(g) 通过氩等离子体处理增强型p沟道薄膜晶体管(TFT)。(h 和 i) 分别为柔性反相器的示意图和照片。

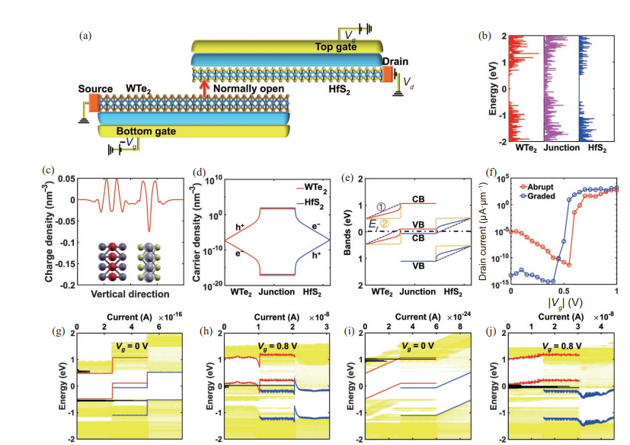

11)新型隧穿场效应晶体管设计与验证:随着半导体技术不断向原子尺度逼近,晶体管的开关性能已接近热电子发射机制的物理极限。进一步突破这一极限并降低功耗,亟需一场技术革新。隧穿场效应晶体管(TFET)凭借其独特的带间隧穿机制,为实现这一目标提供了可能。在TFET中,载流子以“冷”注入的方式进入沟道,避免了传统热注入带来的能量损耗。然而,TFET的性能提升仍面临挑战,尤其是弱隧穿问题,这与能带弯曲程度密切相关,并要求隧穿界面附近具有陡峭的掺杂梯度和强大的栅极调控能力。近年来,机械剥离技术的成功应用催生了一系列具有独特物理和电学特性的新型二维(2D)材料和结构。其中,垂直堆叠的二维材料形成的范德华异质结构(vdWHs)因其无应变、界面清晰且洁净的特性,成为隧穿器件的理想选择。首个栅极调控隧穿的实验验证便是基于p型锗/二硫化钼范德华异质结构的TFET。在该器件中,栅极覆盖整个沟道区域,随着栅极电压(Vg)的增加,电流显著上升。此外,由于在FET特性中栅极参与度较低,具有两侧带隙结构的vdWHs通常被用于构建垂直p-n结。受此启发,团队提出了一种新型的vdWH TFET设计,其栅极调制范围不仅覆盖结区,还扩展至整个器件。该TFET采用III型能带对齐的vdWH,以确保隧穿窗口始终保持开启状态,同时通过单个材料区域的势能调制实现器件的关断与导通。以WTe₂/HfS₂ TFET为例,其沟道由单层WTe₂、HfS₂以及它们的范德华(vdW)结区组成,具有III型能带对齐特性。团队采用第一性原理密度泛函理论(DFT)评估二维材料的电子特性,并结合最大局域化瓦尼尔函数(MLWF)方法,从DFT波函数中构建单元格的紧束缚(TB)哈密顿量。通过扩大vdWH的超胞,突破了最近邻限制,纳入更多键-键相互作用,从而解决了因瓦尼尔轨道局域化不足而导致的精度问题。超胞的扩大尺寸可根据瓦尼尔重构与原始DFT结果之间的能带结构对比进行优化调整。通过首先获得异质结构单元的周期性哈密顿矩阵,再从异质结构中人工提取单层WTe₂和HfS₂的矩阵,同时保持矩阵大小,最终构建了基于DFT-MLWF方法的异质沟道哈密顿模型。仿真结果表明,在结区调节层间电势差存在较大难度,而所提出的沟道势能调制策略在WTe₂/HfS₂范德华异质结构TFET中展现出卓越的开关性能,验证了该策略的有效性。相关论文发表在Science China Information Sciences, 2022, 65, 209401。

图11 (a) WTe₂/HfS₂范德华异质结(vdWH)隧穿场效应晶体管(TFET)的器件模型。(b) 单层WTe₂和HfS₂及其范德华异质结(vdWH)的态密度(DOS),数据来自密度泛函理论(DFT)计算。每种材料的x轴范围为0–4×10³ eV⁻¹。(c) 在考虑层间电荷转移时,垂直方向上的变形电荷密度。(d), (e) 在源极、漏极和栅极电压均为零时,TFET通道的自由载流子和能带结构。图(e)中的红色和蓝色实线表示计算得到的能带,虚线则分别对应突变和渐变的能带极限。(f)–(j) 在漏极电压Vd = 0.3 V时,WTe₂/HfS₂范德华异质结TFET的转移特性及输运细节,其中具有不同的横向结极限:(g), (h) 突变结;(i), (j) 渐变结。在图(g)–(j)中,WTe₂和HfS₂的能带分别用红色和蓝色线条表示。能量分辨的电流谱和参与输运的态密度以黑色线条和背景黄色显示。

12)高增益双极型晶体管设计:双极型晶体管(BJTs)作为电子设备的核心元件,在信号放大、开关电路和振荡器中被广泛应用,是现代电子技术不可或缺的组成部分。然而,传统硅基双极型晶体管由于材料中的缺陷和杂质而面临性能瓶颈。这些缺陷和杂质会导致载流子在穿过集电结时发生背散射,进而产生寄生电流,降低电流增益并增加额外噪声。这种现象在高频应用中尤为显著,严重影响信号完整性。此外,高性能双极型晶体管的制造需要复杂的工艺,例如精确的掺杂控制和精细的层结构设计,这不仅限制了其集成密度,也阻碍了进一步的微型化。因此,要实现双极型晶体管的突破性进展,必须在材料和制造工艺上进行重大改进。基于异质结构的二维(2D)半导体为解决这些挑战提供了一种潜在的解决方案,能够有效抑制原子扩散和位错传播等问题。例如,采用二硫化钼(MoS₂)/二硒化钨(WSe₂)/二硫化钼(MoS₂)异质结构的双极型晶体管已展现出高达α = 0.97和β = 1214的电流增益,这主要得益于其原子级厚度的基区。然而,进一步优化MoS₂/WSe₂/MoS₂双极型晶体管仍面临挑战,主要受限于弱电流调制能力,同时异质结构的复杂制造工艺也限制了其实际应用。此外,二维半导体的原子级厚度使其成为热电子晶体管(HETs)中超薄金属基区的理想替代材料。此前的研究表明,基于二维半导体基区的热电子晶体管能够实现α = 0.95和β = 10的电流增益。然而,热电子晶体管通常需要额外的势垒层或隧穿层来发射高能电子,这不仅增加了制造工艺的复杂性,还导致成本上升和生产周期延长。更严重的是,热电子可能会从半导体材料中散射逸出,而不是通过基区传导至集电区,从而导致漏电流增加,并可能损坏封装介质材料。因此,开发具有简化结构的高性能、高电流增益二维双极型晶体管显得尤为迫切。团队提出了一种基于金属-半导体接触的二硫化钼(MoS₂)双极型晶体管。通过将高功函数金属铂(Pt)与多层二硫化钼形成肖特基接触,构建了一个能够实现电子热电离发射的发射极-基极结,以及一个利用肖特基二极管内建电场收集电子的集电极-基极结。此外,载流子传输主要在二硫化钼中进行,从而显著减少了因杂质和缺陷引起的寄生电流。该MoS₂双极型晶体管实现了0.99的共基极电流增益和1967的共发射极电流增益。与传统硅基双极型晶体管以及其他二维半导体双极型晶体管相比,团队制备的MoS₂双极型晶体管具有更简单的制造工艺,无需复杂的掺杂或介质层制备。这些优势使其在高性能应用中展现出巨大的潜力。相关论文发表在Nano Letters, 2024, 25(1): 204-211。

图12 基于肖特基接触的二硫化钼双极型晶体管。(a) 基于金属-半导体肖特基接触的二硫化钼双极型晶体管(BJT)器件的示意图。(b) 器件的光学显微镜图像。左下角插图显示原子力显微镜(AFM)图像,右上角插图显示扫描电子显微镜(SEM)图像。(c) 不同温度下铂(Pt)/二硫化钼肖特基结的电流-电压(I-V)特性。插图I展示了Pt/二硫化钼肖特基结的截面示意图,插图II展示了相应的能带图。(d) 在不同电压下,ln(I/T²)与1000/T的关系图。(e) 在不同电压下提取的斜率曲线。

13)双层堆叠电介质高性能晶体管设计:随着器件微型化不断逼近其基本物理极限,传统的沟道材料已难以满足进一步发展的需求。因此,新型替代材料具有原子级厚度的二维(2D)层状材料应运而生。这些材料即使在沟道长度仅为1 nm的条件下,仍能展现出卓越的电学性能。通常情况下,晶体管的阈值电压主要由栅极介质的厚度和相对介电常数决定。为了实现低压操作,超薄高介电常数(高k)氧化物介质被广泛采用,因为它们能够显著增强静电栅极控制能力。然而,由于二硫化钼(MoS2)表面缺乏足够的悬挂键或成核位点,将介电层均匀沉积在其表面仍然面临挑战。相比之下,溶液加工的高k聚合物介质(如聚偏二氟乙烯-三氟乙烯,P(VDF-TrFE))因其优异的性能,被广泛认为是基于二维材料晶体管的理想介质层。然而,这些材料仍存在一个严重的缺陷:由栅极偏压诱导的局域态会导致大量电荷被困在二维材料与介质的界面处。即使在惰性环境中,这种现象也会导致阈值电压显著漂移,从而严重影响器件的稳定性。为解决这一问题,低k非极性聚合物介质(如聚甲基丙烯酸甲酯,PMMA)被引入。PMMA作为一种低k疏水介质,能够有效消除水分、氧气、可动电荷以及其他杂质的影响,从而实现无迟滞操作。然而,这种材料的缺点在于无法支持低压操作。为兼顾高性能与稳定性,双层堆叠介质方案应运而生。在这种设计中,高k介质通过高栅极电容在沟道中诱导高载流子密度,而低k介质则为器件提供了稳定的运行特性。在此基础上,团队采用低k的PMMA与高k的P(VDF-TrFE)组成的双层堆叠介质,成功实现了低压操作、无迟滞特性以及长期稳定的高性能二硫化钼(MoS2)晶体管。通过这种设计,界面陷阱密度和阈值电压分别降低至7.0×1011 cm-2 ·eV-1和−2.2 V。因此,团队提出的策略为制造低功耗、无迟滞且稳定性卓越的基于二维材料的晶体管提供了一种极具潜力的解决方案。相关论文发表在IEEE Electron Device Letters, 2020, 41(7): 1036-1039。

图13 (a) 顶栅二硫化钼(MoS₂)晶体管的示意图,展示了不同栅极介质层:聚(偏二氟乙烯-三氟乙烯)[P(VDF-TrFE)]、聚甲基丙烯酸甲酯(PMMA)以及PMMA/P(VDF-TrFE)双层介质。(b) 光学显微镜图像显示了二硫化钼(MoS₂)与金属电极之间的接触,插图为整个MoS₂晶体管的全局图像。(c) 介质层的铁电极化特性。(d)-(f) 不同栅极介质的MoS₂晶体管的典型转移曲线。红线、黑线和蓝线分别对应漏极电压(Vᴅ)为1 V、0.5 V和0.1 V。插图放大显示了在Vᴅ = 1 V时的转移特性曲线。